如要使用数据流模型执行代码,LabVIEW将同步FPGA上的逻辑。默认情况下,LabVIEW FPGA在程序框图的逻辑函数间放置一个寄存器,以最大化每个操作执行所需的传播时间。

传播延时是指信号由一个寄存器传播至下一个寄存器所需的时间。组合路径是信号由一个寄存器经另一个寄存器的逻辑和接线的集合。

由于每个时钟周期均更新寄存器内容,因此传播延时必须小于时钟周期。传播延时由两部分组成:逻辑延时和连线延时。逻辑延时是信号经过的逻辑门数量和类型的函数,通常表示传播延时中最重要的组件。连线延时是信号通过的连线路径的函数,其通常很小。因为FPGA编译器尝试尽可能紧密的集合组合路径的组件。但当FPGA VI达到FPGA的容量限制时,函数间的物理间隔将增加。同时连线延时将成为两个寄存器间总体传播延时的主要组成部分。如两个寄存器间的传播延时大于FPGA时钟速率,FPGA编译器将返回定时错误。该定时错误称为时间限制或周期限制冲突。

注: 给定函数的逻辑延时随终端变化。连线延时在每次FPGA VI编译时均发生变化。

LabVIEW FPGA模块专用于生成可在单周期定时循环外部以至少40 MHz的时钟速率运行的电路。40 MHz时钟速率对应的是25 ns的时钟周期。为了避免2个寄存器间的传播延时超出25 ns,多数LabVIEW函数均包含一个输出寄存器,因此需要一个完整的时钟执行周期。如2个寄存器间的传播延时超出了25 ns,FPGA VI无法在40 MHz默认的时钟速率完成编译。

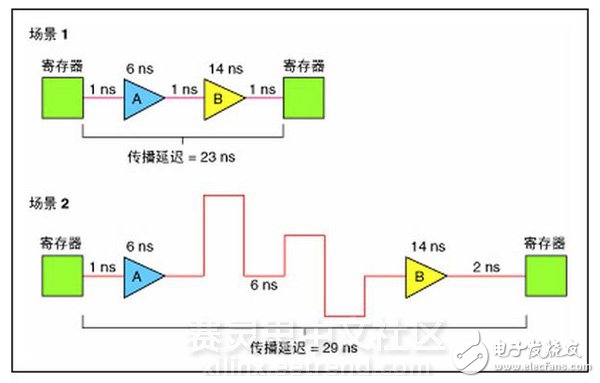

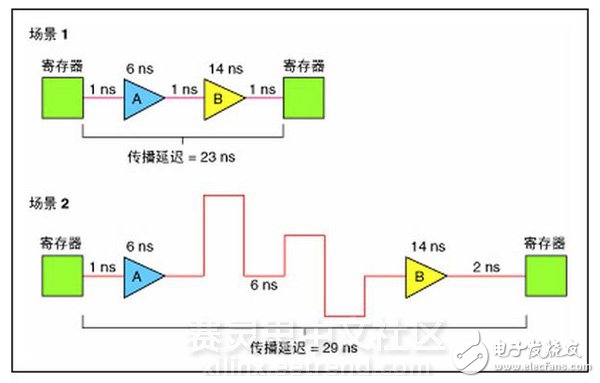

例如,假设函数A需要6 ns的逻辑延时,函数B需要14 ns的逻辑延时。如顺序连线函数A和B,而不在函数间添加寄存器。整体逻辑延时为20 ns。如要在40 MHz的默认时钟速率下完成编译,连线延时只能为5 ns。根据FPGA编译器在函数间的连线方式,连线延时可能超出或不超出5 ns。如下列场景和1和2所示。

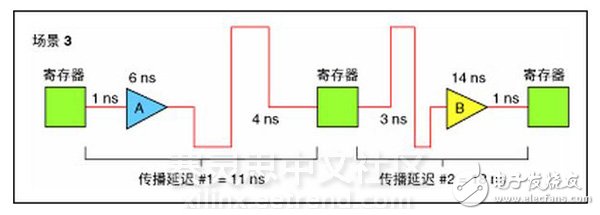

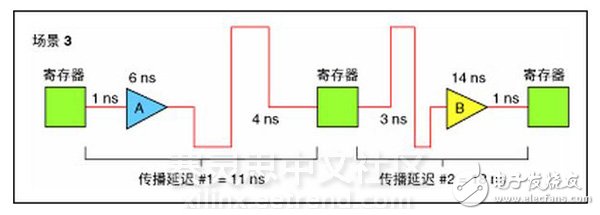

在场景1中,设计满足40 MHz的定时限制。在场景2中,设计不满足40 MHz的时钟限制。当用户尝试编译FPGA VI时将产生定时冲突错误。相比之下场景3中,2个函数之间添加了寄存器。添加寄存器后将产生2个独立的传播延时。即使连线路径较长,2个传播延时均可实现在40 MHz内完成编译。

当函数位于单周期定时循环外时,FPGA编译器将在函数的逻辑级间均匀放置寄存器,以将逻辑划分为可在默认FPGA时钟速率内执行的部分。如函数包含运行在FPGA上的内部寄存器(例如,存储器方法节点),函数的执行时间周期数量与函数寄存器数量相等。

如在同一时钟速率下,需要以较小的延时执行逻辑可使用单周期定时循环。如在单周期定时循环内放置函数,编译器不会包含用于该函数的输出寄存器,因此单周期定时循环可在一个时钟周期内完成。某些函数(例如窗函数缩放或FFT Express VI),即使当其位于单周期定时循环内部时,也需要多个时钟执行周期。握手机制可用于管理上述函数的数据定时。

如单周期定时循环内的传播延时大于时钟周期,定时冲突分析窗口将指出未能满足定时要求的单周期定时循环。在某些情况下,可使用反馈节点或移位寄存器缩短组合路径的长度,以实现流水线设计。

注: 如在单周期定时循环内使用高吞吐率数学函数,用户可添加内部寄存器缩短函数间的组合路径长度。

大型FPGA应用的资源考虑

每个FPGA终端包含一定数量的触发器。由于寄存器使用触发器,用于FPGA VI的寄存器数量和类型将决定FPGA VI是否能够满足FPGA终端的需求。通常寄存器使用的触发器数量与数据类型宽度相对应。例如,布尔寄存器仅需要一个触发器来存储数据,而一个I64寄存器需要使用64个寄存器来存储数据。

对于多数用户来说,FPGA上有限的触发器数量并不是问题。但如FPGA上的资源耗尽,则需要优化FPGA VI的大小。

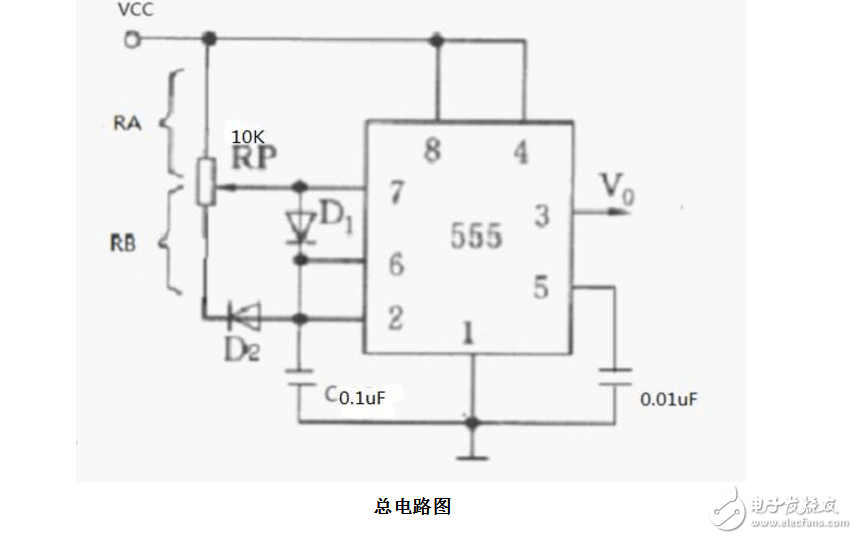

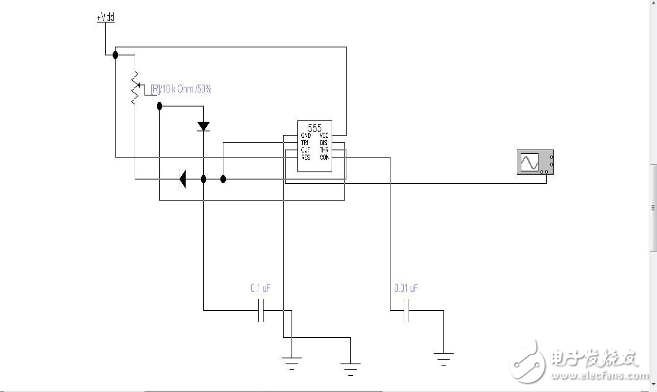

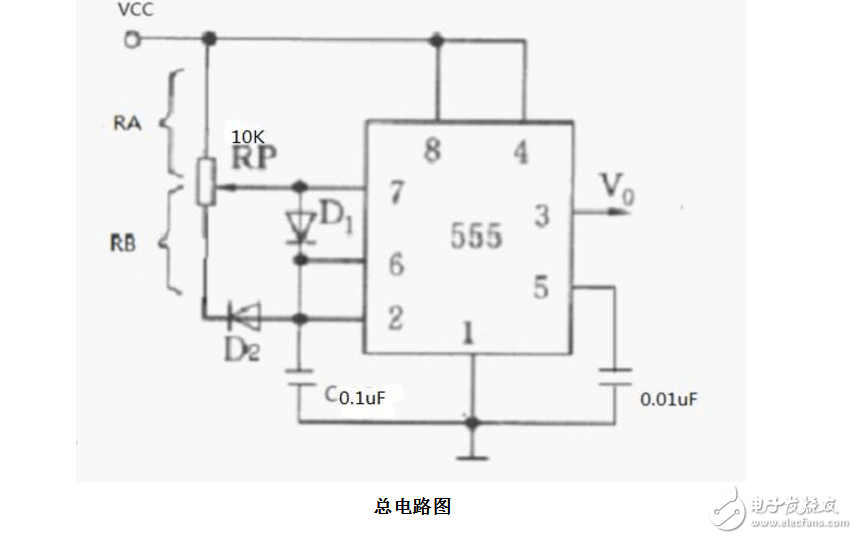

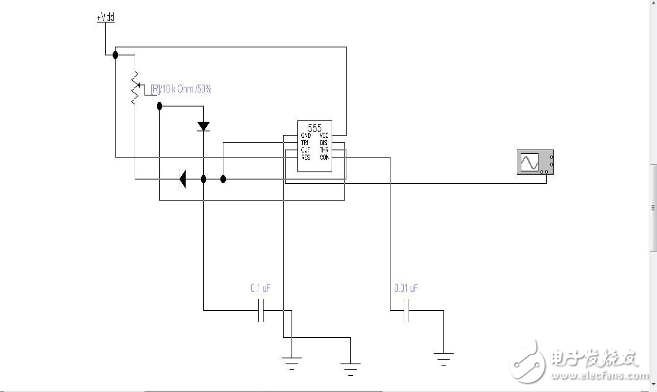

方波信号发生器工作原理

由集成运放构成的方波发生器,包括迟滞比较电路和RC积分电路两大部分。因为矩形波电压只有两种状态,不是高电平,就是低电平,所以电压比较器是它的重要组成部分;因为产生振荡,就是要求输出的两种状态自动地相互转换,所以电路中必须引入反馈;因为输出状态应按一定的时间间隔交替变化,即产生周期性变化,所以电路中要有延迟环节来确定每种状态维持的时间,即RC 积分电路。

根据555定时器改变阀值电压的值使之输出高电平或低电平的原理,就可以产生方波,通过电位器改变电阻的阻值来控制高低电平的时间就可以调节占空比了;通过调节输入的电压值,再通过万用表测量输出的电压值就可以保证输出幅度为某一定值;根据振荡频率公式,已知电阻值和输出振荡频率就可以算出需要电容值,以保证振荡频率为某一定值;为保证波形稳定,采用差分电路形式,用555定时器组成的多谐振荡器的振荡频率受电源电压和温度变化的影响很小;而为了简化电路及运算,采用两个二极管的单向导电特性,使电容器的充放电回路分开,回路不再重复,计算更加简便。

占空比可调的方波发生器

(1)输入模块

二极管D1,D2的单向导电性,使电容器C的充放电回路分开,调节电位器,就可以调节多谐振荡器的占空比。

(2)处理模块:

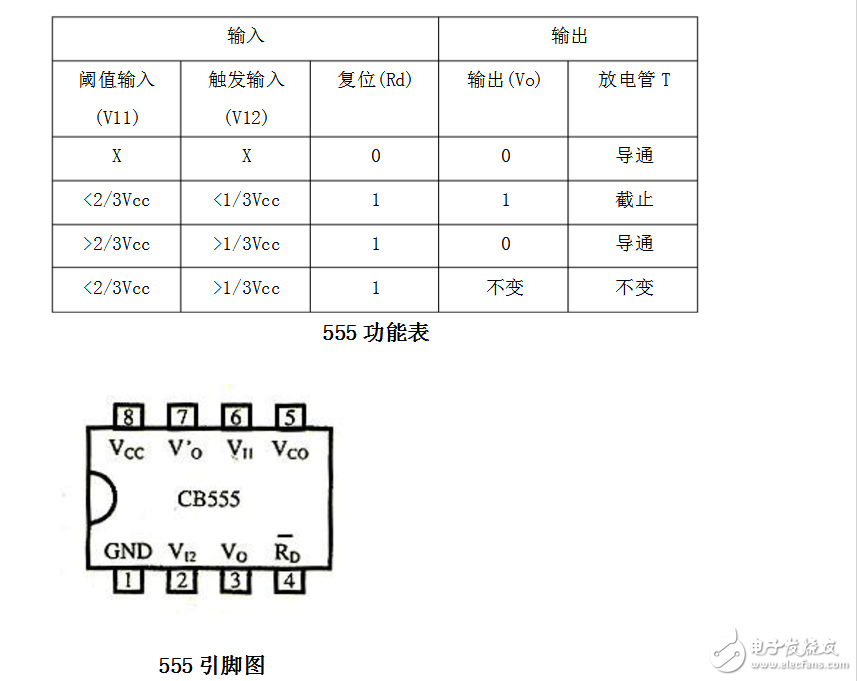

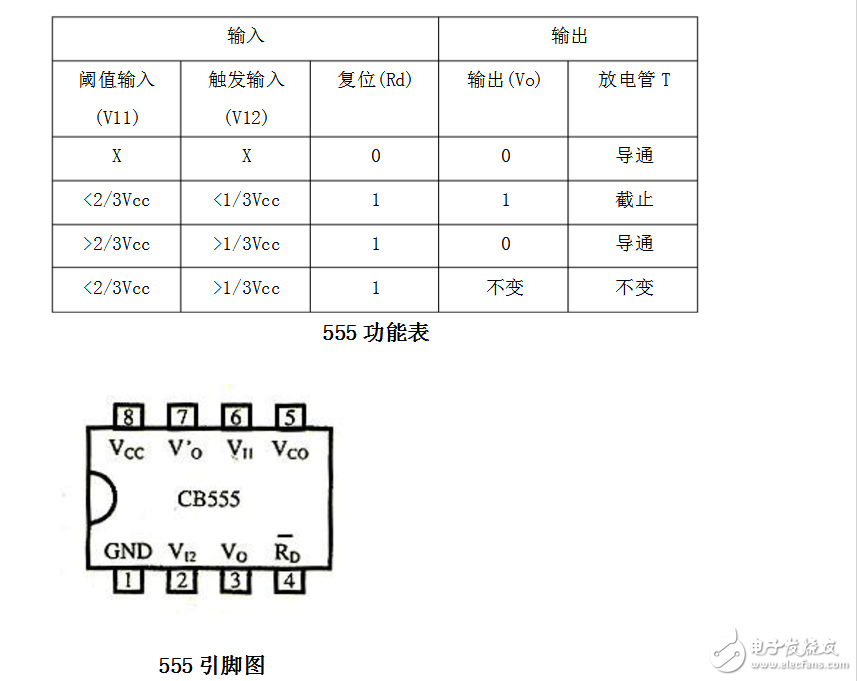

555定时器各引脚功能如下:

1脚:外接电源负极或接地(GND)。

2脚:TR触发输入。

3脚:输出端(OUT或Vo)。

4脚:RD复位端,移步清零且低电平有效,当接低电平时,不管TR、TH输入什么,电路总是输出“0”。要想使电路正常工作,则4脚应与电源相连。

5脚:控制电压端CO(或VC)。若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。

6脚:TH高触发端(阈值输入)。

7脚:放电端。

8脚:外接电源VCC(VDD)。

(3)输出模块:

与上处理模块555的3脚输出端相连

(4)总

电路只要一加上电压VDD,振荡器便起振。刚通电时,由于C上的电压不能突变,即2脚电位的起始电平为低电位,使555置位,3脚呈高电平。C通过RA、D1对其充电,充电时间t冲=0.7RAC。压充到阈值电平2/3 VDD时,555复位,3脚转呈低电平,此时C通过Dl、RB、555内部的放电管放电,放电时间t放=0.7RBC。则振荡周期为T=t冲+t放。

(5)设计目标:设占空比为D,则D=t冲/t放=RA/(RA+RB)=RA/RP,调节定位器RP,当其中心头滑向最上端时,D=RA/RP=0/10K=0;当RP1中心头滑向最下端时,D=RA/RP=10K/10K=100%

(6)确定参数:由技术要求中振荡频率f=10KHz及f=1.43/(RA+RB)C=1.43/

得电容C的取值为0.143uF,我们使用的是C=0.1uF。

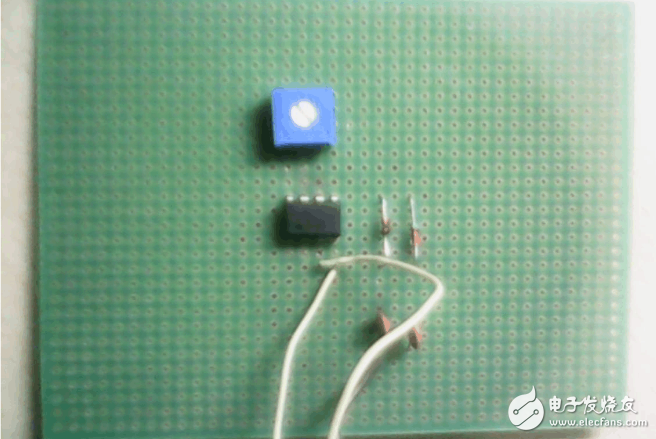

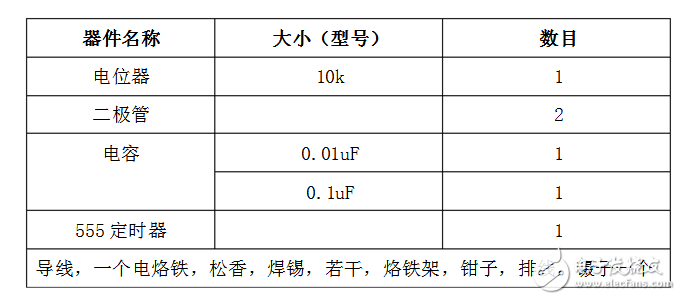

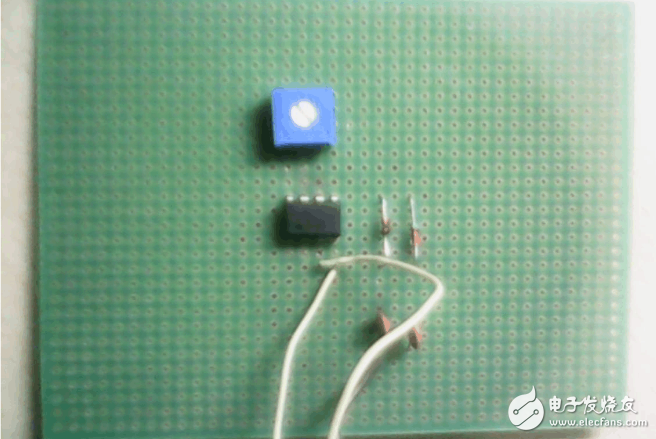

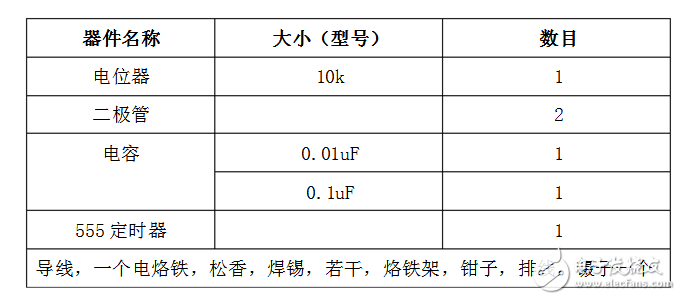

占空比可调的方波发生器硬件制作

(1)依照原理图将各个元器件安放在电路板上并布局。

(2)进行焊接。焊接过程中要边焊接边检查,防止漏焊、连焊。

电路测试

(1)检查电路中各个元件是否接的可靠、大小是否合理,特别是NE555必须接正确。

(2)在一切都正常的情况下,给电路提供+12V电源,此时立即触摸NE555是否发烫,若发烫应立即断电。

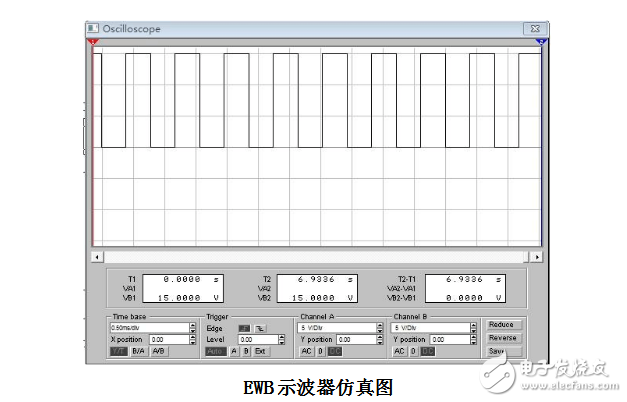

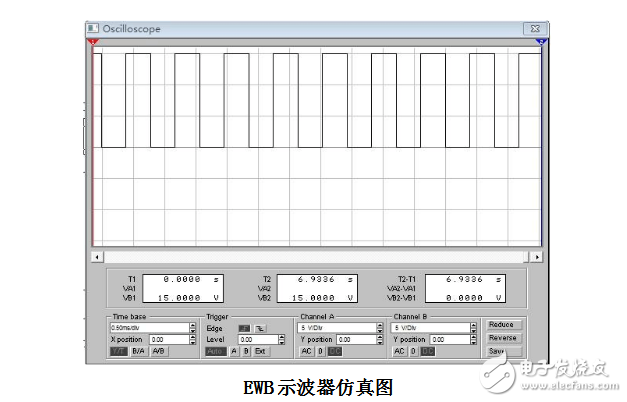

(3)若NE555没有发烫,则说明NE555工作正常,这时开始实验数据测试 。 (4)通过示波器观察NE555输出的方波信号。 (5)观察结束后,断电。